什么是锡须?

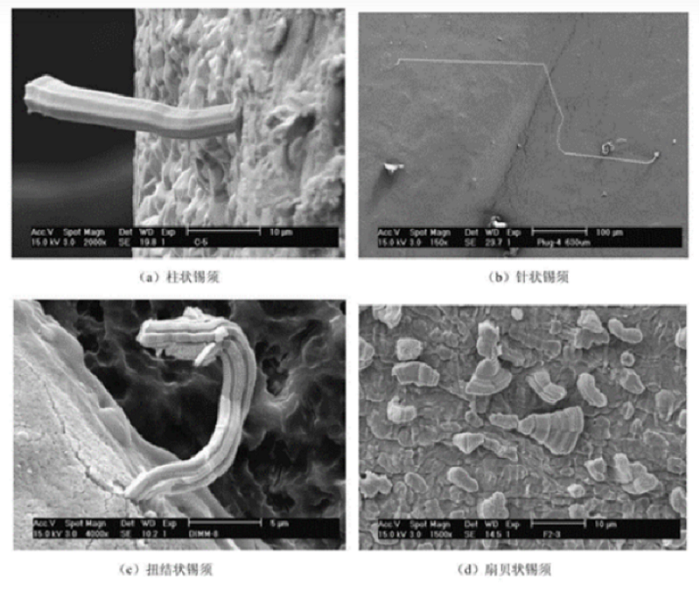

锡须是电子元器件焊接表面上可能生长的细小锡晶须,这种生长可能导致电路短路、故障甚至失效。锡须的形成对电子设备和电路板构成多种潜在危害,包括短路风险、信号干扰、绝缘破坏、热量积累和环境污染。

锡须是电子元器件焊接表面上可能生长的细小锡晶须,这种生长可能导致电路短路、故障甚至失效。锡须的形成对电子设备和电路板构成多种潜在危害,包括短路风险、信号干扰、绝缘破坏、热量积累和环境污染。

锡须试验的目的

锡须试验的目的是模拟元器件在高温高湿环境下的运行情况,评估元器件焊点是否会产生锡须,从而影响其可靠性。锡须的存在可能会对电子设备和电路板产生一些危害,如短路风险和信号干扰。金鉴实验室提供的锡须试验服务,能够有效模拟各种环境条件,帮助制造商识别潜在问题,提高产品的可靠性。

锡须的形成机理

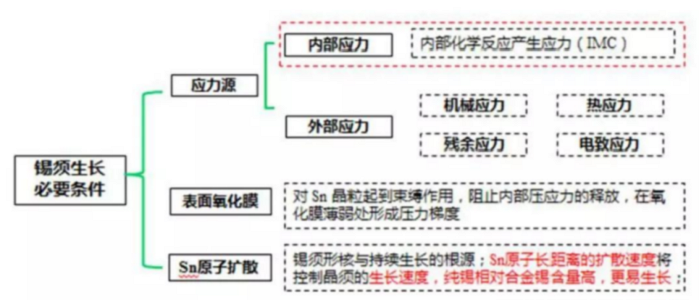

锡须的生长是一种应力梯度作用下的室温蠕变行为,需要具备应力源、氧化层束缚和Sn原子长范围扩散三个条件。锡须生长的驱动力主要为内部的内应力,如Cu/Sn界面间形成的金属间化合物Cu6Sn5对锡层产生的压应力。

锡须的生长过程

锡须的生长可以分为五个过程:Cu/Sn结合界面的原子相互扩散、晶界效应、压应力的产生、IMC层的持续生长和Cu6Sn5层反应减缓。锡须的生长可分为孕育期、快速生长期和低速生长至停止期三个阶段。

锡须试验过程

锡须试验是一个长期可靠性问题,需要找到合适的加速试验方法及加速因子。JESD22-A121提供了锡须生长的可靠性加速试验参考、锡须长度测试方法和失效评判依据等。试验过程包括对多引线元件的不同lots样本进行前置条件处理,在不同时间点检查端子,测量锡须长度,并在不同条件下执行试验。金鉴实验室在锡须的检测与评估方面积累了丰富的经验,能够为客户提供全面的风险评估和解决方案,保障电子产品的安全性和可靠性。

抑制锡须的方法

抑制锡须的方法包括使用合金镀层替换纯锡镀层、退火处理、在Cu上镀Ni后再镀Sn、选择合适的镀层厚度和优化镀液和镀敷工艺。金鉴实验室的专家团队能够根据客户的具体需求,提供定制化的锡须分析方案,帮助企业提升产品质量,降低生产风险。

2024-2025(c)版权所有深圳市易方时代科技有限公司

联系人:林经理 手机:18379413502

邮箱:736615361@qq.com 网址:www.zhykby.cn

地址:深圳市福田区华强北街道中航路新亚洲电子商城一期4C011A

|

| 手机版 |